Combinational logic의 두 번째 유형, 산술연산 로직에 대해 다뤄보겠습니다.

'산술연산' 로직은 덧셈이나 뺄셈 같이 산술적인 계산을 하는 로직을 가리킵니다. 숫자를 입력받아 숫자를 출력하는 로직입니다.

가장 대표적인 예로는 half adder와 full adder가 있습니다.

두 adder의 차이점은 'carry 입력'(위 그림에서는 Ci 포트)의 유무에 있습니다.

1-bit full adder는 입력 포트로 받을 수 있는 최대값이 1에 불과하기 때문에 그다지 실용적이지 않습니다. 이걸로는 2+3 같은 계산조차 할 수 없으니까요. 이제 입력포트 A, B의 폭을 3비트로 늘려봅시다. 3비트짜리 두 값을 받아서 더하고 그 결과를 출력해야 합니다. 이 로직은 어떻게 만들 수 있을까요?

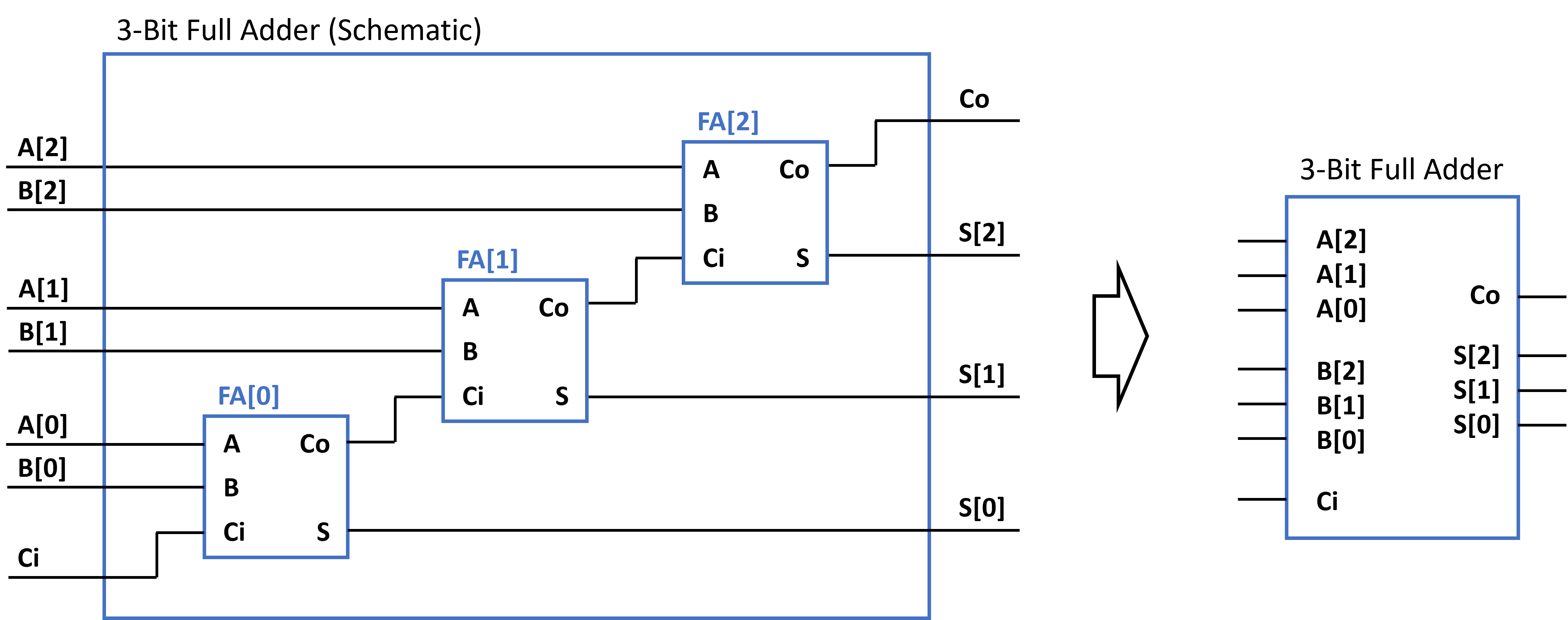

A, B 포트를 통해 받은 입력값을 각 자리(비트 위치)마다 따로 더해주면 되겠죠. 만약 자리올림이 있으면 바로 다음 자리(상위 비트)에서 그것까지 같이 더하고요. 아래 그림과 같이 1-bit full adder를 비트 수만큼 연결해 3-bit full adder를 구성할 수 있습니다.

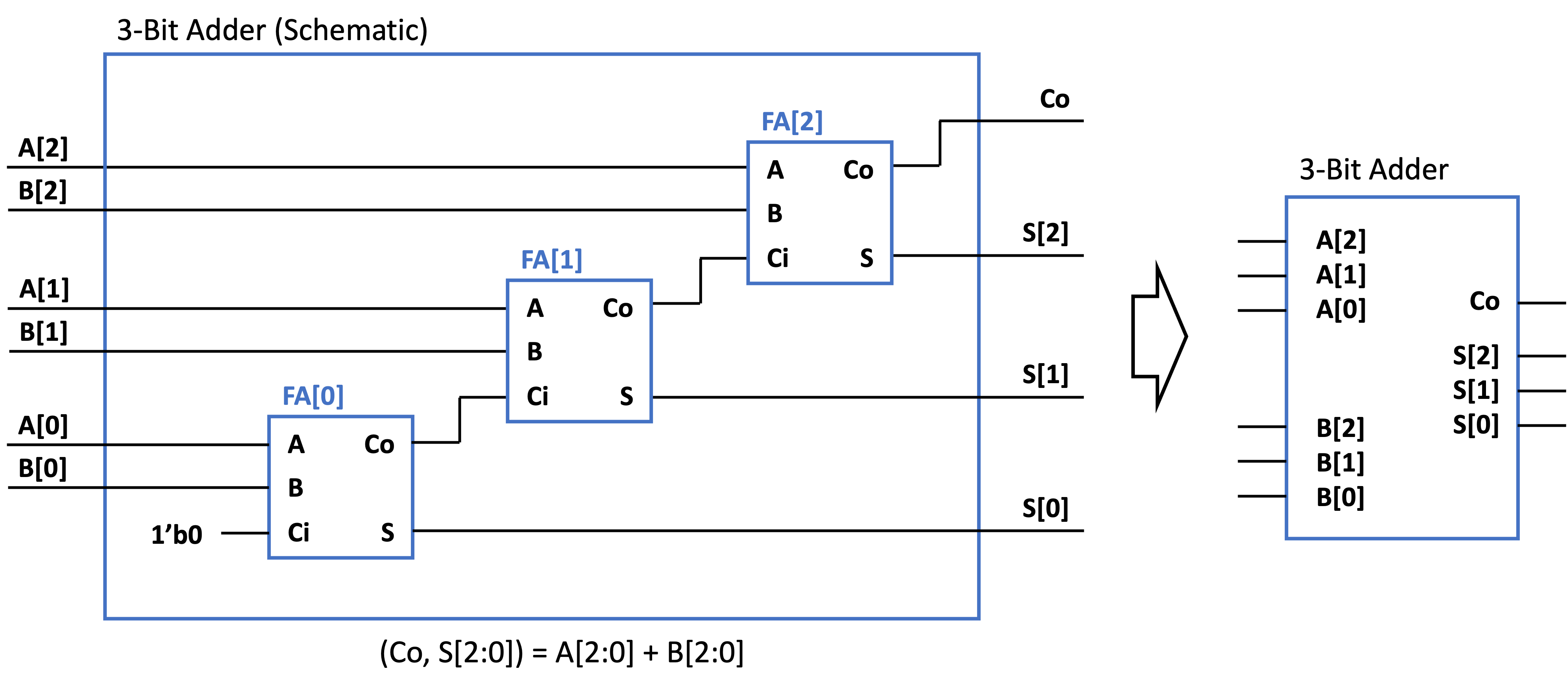

자리올림을 고려할 필요가 없다면, 아래 그림처럼 캐리 입력(Ci)을 0으로 고정시켜도 됩니다.

입력 포트가 하나 줄어서 좀 더 간단해 보이죠.

여기까지 산술연산 유형의 로직에 대해 알아 보았습니다. 다음은 마지막 유형, '흐름제어'입니다.

목차 (연재 순서)

0. 강의 개요

1. 기초 논리 소자 (Basic Logic Elements)

2. Combinational Logic

1) 논리연산 -- 3-input AND, 2-input XOR

2) 산술연산 -- Half Adder, Full Adder

3) 흐름제어 -- Mux, Demux

3. Truth Table 및 Look-Up Table

1) 우리는 어떤 목적으로, 왜 truth table을 작성하는가?

2) 설계한 로직은 어떻게 FPGA에서 작동하는가?

4. 메모리 소자 (Memory Elements)

1) Flip-Flop

2) Memory Block

5. Sequential Logic

1) D-FF with synchronous reset

2) 2진법 반올림(round-up) 로직

6. Timing Diagram

'강의' 카테고리의 다른 글

| [디지털 로직 설계] - #6. Truth Table 및 Look-Up Table (0) | 2024.05.15 |

|---|---|

| [디지털 로직 설계] - #5. 흐름제어 (0) | 2024.05.07 |

| [디지털 로직 설계] - #3. 논리연산 (0) | 2024.04.16 |

| [디지털 로직 설계] - #2. Combinational Logic (0) | 2024.04.16 |

| [디지털 로직 설계] - #1. 기초 논리 소자 (Basic Logic Elements) (0) | 2024.04.09 |